반응형

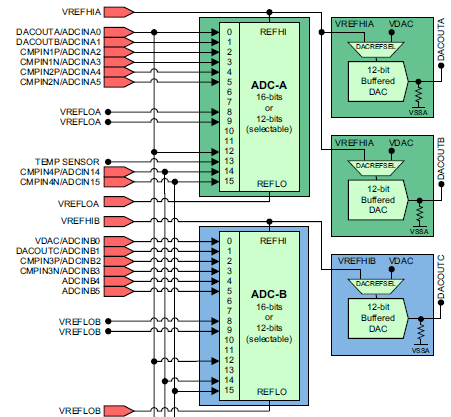

DAC 겸용 채널인 ADCINA0, ADCINA1, ADCINB1의 경우 내부의 50k옴 풀다운이 있다.

해당 채널을 ADC로 사용시 영향성은? 만약 ADC 입력 단에 높은 값의 저항이 있다면 전압분배기를 형성하여 게인 오류를 일으킬 수 있다고 한다.

그리고 데이터시트를 찾아보면 ADC 입력 회로의 소스 임피던스에 대한 언급도 있다. 이건 모든 ADC 채널에 적용되는건데, 아래 그림에서 소스 임피던스 Rs와 Ron의 합성저항은 ADC 내부의 샘플링 앤 홀드 커패시터인 Ch와 RC회로를형성하는데 Rs값이 커지면 Ch의 충전 시간 상수가 커져서 Ch가 목표 전압에 도달하는 데 더 오랜 시간이 걸린다고 한다.

즉, Rs의저항이 크고 샘플링 시간이 충분하지 않은 경우 Ch가 입력 전압에 완전히 도달하지 못하고 샘플링이 종료되어, 이로인해 ADC 출력 값이 예상보다 낮게 나올 수 있다.

반응형

'임베디드 개발 > TMS320F2838x (C28x)' 카테고리의 다른 글

| CCS ] .out(ELF) 파일에서 섹션 정보 파싱하기 (0) | 2024.12.07 |

|---|---|

| TMS320F28388D ] 링커커맨드 파일과 컴파일러 섹션 (0) | 2024.08.16 |

| TMS320F28388D ] Input Qualification (0) | 2024.07.02 |

| ccs 프로젝트 빌드 과정 (0) | 2024.06.12 |

| TMS320F28388D ] 다중 ADC 사용시 변환 순서와 동기 (0) | 2024.05.01 |