다중 ADC 사용시 변환 순서와 동기에 대해 알아보는데 의식의 흐름순으로 작성되었다.

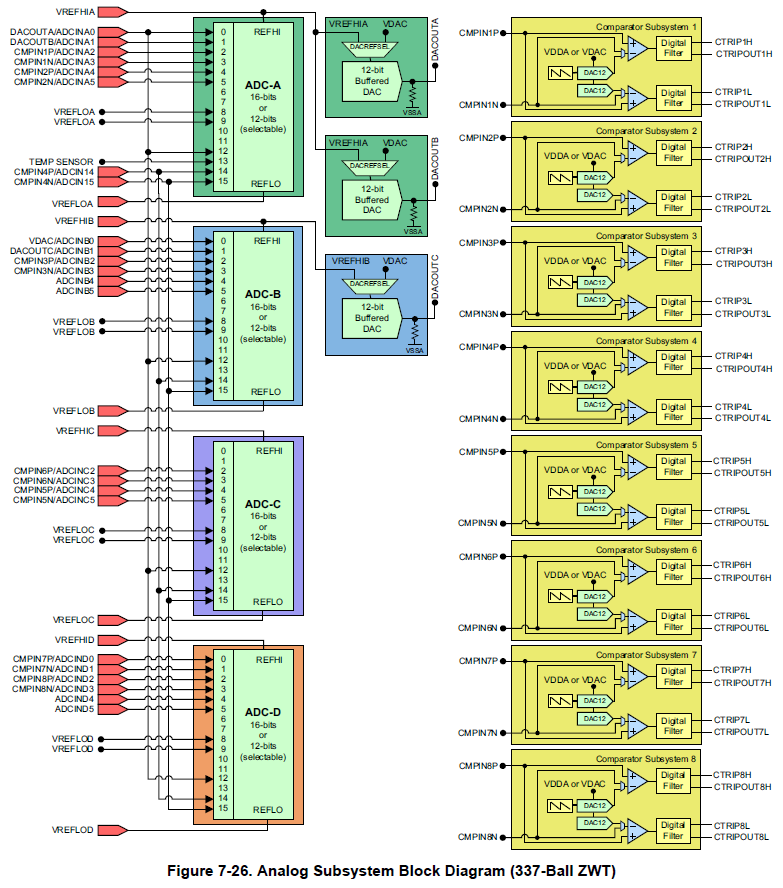

먼저 사전 설명을 하자면 TMS320F28388D 337-Ball ZWT 패키지는 Temp Sensor를 제외하고 총 24채널의 ADC 입력을 처리할 수 있다. 근데 그중에 3개(ADCINA0, ADCINA1, ADCINB1) 채널은 DAC 용도로도 사용된다. 예를 들어 DAC 3채널을 쓰면 ADC는 21채널만 쓸 수 있는거다.

DSP의 ADC 모듈은 총 4개가 있다. ADC-A, ADC-B, ADC-C, ADC-D.

그리고 Temp Sensor는 DSP에 내장되어 있고 ADC-A 모듈과 이미 연결되어 있다. TI가 제공한 예제를 사용하면 쉽게 칩의 온도를 읽을 수 있다.

아래 그림은 ADC 모듈 블럭이다. ADC 모듈에는 S/H Circuit과 AD Converter가 하나만 있으므로 한번에 하나의 채널만 변환할 수 있다. 한편 ADC 모듈 내에는 16 개의 SOCx(Start of Conversion)가 있고, SOCx에 각각에 대해 트리거 소스를 설정하고 CHSEL 레지스터를 통해 물리적 입력핀(ADCINx)과 매핑하며 ACQPS 레지스터를 통해 S+H time을 설정할 수 있는 구조를 가지고 있다.

이 때 하나의 트리거 소스로 여러 SOC를 트리거하면 SOC의 우선순위에 따라 순차적으로 ADC를 진행하는 구조이다. 그리고 SW에선 그 중 마지막 SOC의 변환종료(EOC, End of Conversion) 신호로 인터럽트를 발생시켜 모든 SOC의 ADC 결과를 획득할 수 있다.

이는 다만 한 ADC 모듈에 국한된 얘기는 아니다. 예를 들어 ADCA는 SOC0-SOC5를 사용하고 ADCB는 SOC0-SOC4를 사용하고 ADCC는 SOC0-SOC3을 사용한다고 했을 때, 모든 ADC 모듈의 ADCCLK이 동일하고 모든 ADC 변환이 하나의 트리거 소스에서 발생하며, 동일한 S+H time을 갖는다면 ADCA의 SOC5의 변환종료(EOC) 시그널에 맞춰 ADCA, ADCB, ADCC 모든 모듈의 결과값을 전부 획득하는 방식이 가능하다.

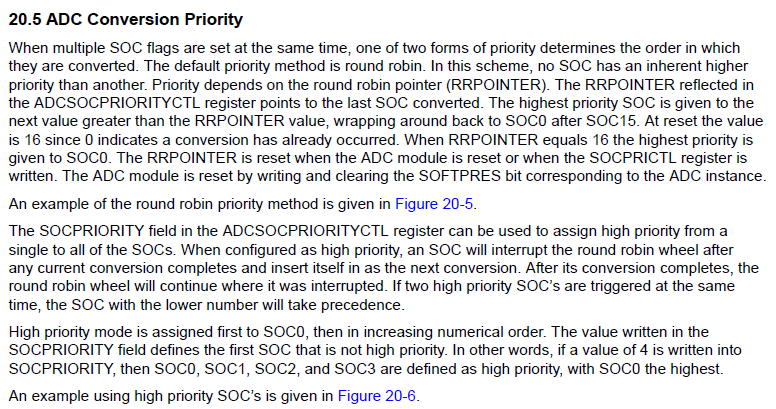

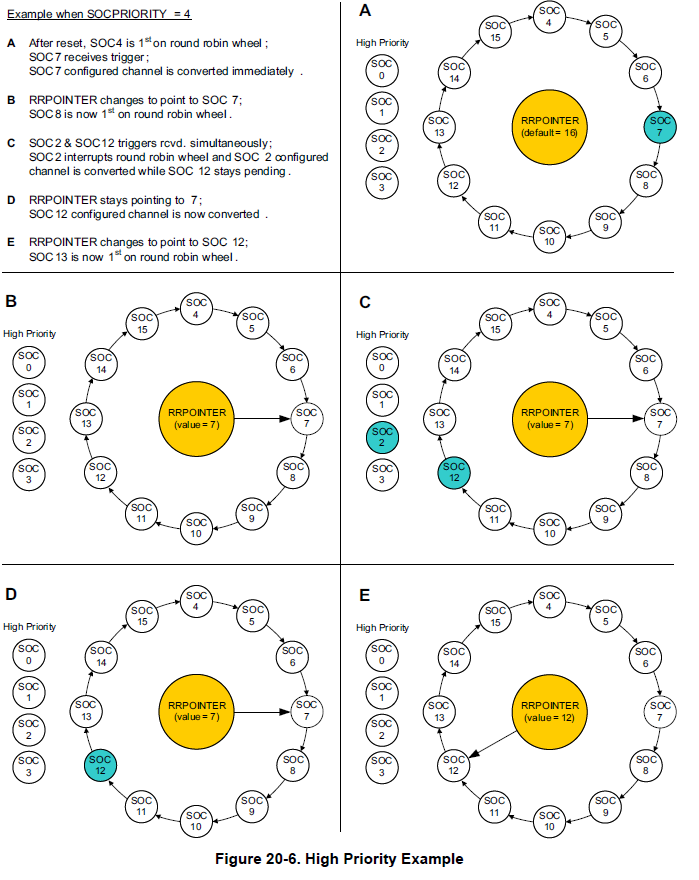

아무튼 다시 본문으로 돌아가서 여러 SOC가 하나의 트리거 소스를 통해 동시에 트리거 되었을 때 변환의 우선 순위 결정 방식은 1. Round Robin 방식과 2. High Priority 방식 두 가지가 있다.

1. Round Robin 방식

SOC 플래그는 모드 동등한 우선순위를 가지고 순서대로 처리된다. RRPOINTER는 마지막으로 변환된 SOC를 가르키는데 만약, RRPOINTER = 7이면 SOC8이 가장 높은 우선순위를 갖는다. 이때 SOC2와 SOC12가 동시에 트리거되면 SOC12가 먼저 처리되고 그 다음 SOC2가 처리되는 방식이다. RRPOINTER의 리셋시 초기값은 16이고 이 때의 우선 순위는 SOC0이 가진다.

2. High Priority 방식

특정 SOC에 고정된 높은 우선순위를 할당하여 라운드 로빈 순서를 방해하고 특정 SOC 변환을 우선 수행할 수 있다. SOCPRIORITY에는 우선순위를 갖지 않는 첫번째 SOC를 정의하면 되는데 만약 SOCPRIORITY 값이 4라면 SOC0, SOC1, SOC2, SOC3 순서로 고정 우선순위를 가진다.

근데 사실 알아보는 의미가 별로 없는게 보통 Round Robin 방식을 사용할 것 같다. ePWM이든 CPU Timer든 SW 트리거든 간에 다음 트리거가 도착하기 전에 모든 SOC 변환이 완료된다면, 다음 트리거가 왔을 때 ADC모듈은 처음부터 SOC 변환을 시작하게 되고 항상 동일한 순서로 이루어질 것이기 때문이다. 따라서 트리거의 간격이 충분하다면 SOC 변환 순서의 일관성에 대해 크게 걱정할 필요가 없을 듯 하다.

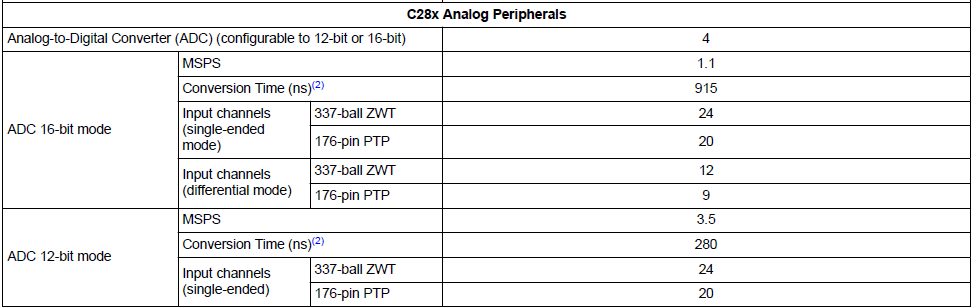

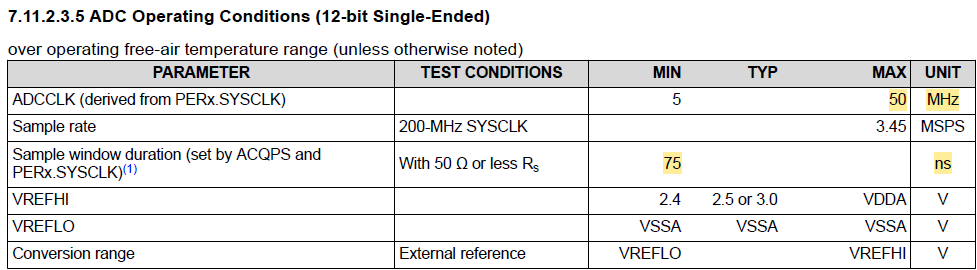

그럼 SOC 변환이 얼마나 걸리는지도 알고 있을 필요가 있겠다. TMS320F28388D의 데이터시트를 확인하면 ADC의 성능 지표중 하나인 MSPS 값이 16-bit mode는 1.1 MSPS, 12-bit mode는 3.5 MSPS라고 한다.

(❗MSPS란? 초당 몇번 샘플링 하는지는 Sample Per Second라고 하는데 만약 어떤 ADC의 스펙이 1 MSPS라면 1us당 1번 샘플링이 가능하단 뜻이며 1초당 백만개의 데이터가 나오는 것이다.)

그리고 그 밑에 Conversion Time(ns)가 나오는데 16-bit ADC는 915ns, 12-bit ADC는 280ns라고 되어있다. 헷갈릴 수도 있는데 여기서 말하는 Conversion Time은 (Sample and Hold duration + ADC Processing Block의 Conversion Time)을 합친 시간이다.

S+H duration을 먼저 보면 16-bit mode의 경우 320ns, 12-bit mode의 경우 75ns로 데이터 시트에 나와있다.

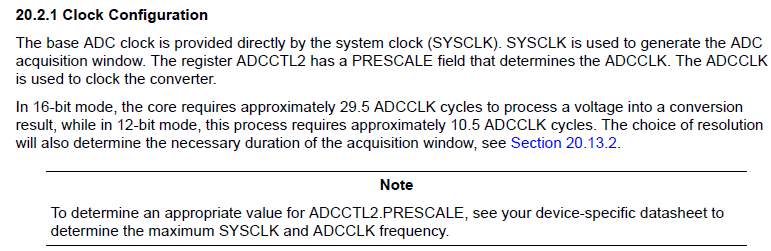

그다음 ADC Processing Block의 Conversion Time은 16-bit mode의 경우 29.5 ADCCLK, 12-bit mode의 경우 10.5 ADCCLK로 TRM에 나와있다. 그리고 ADCCLK의 MAX값은 50MHz이므로 결국 Conversion Time 16-bit mode의 경우 590ns, 12-bit mode의 경우 210ns가 소요된다.

다시 총 변환시간으로 돌아가면 16-bit ADC는 910ns = 320ns + 590ns이고, 12-bit ADC는 285ns = 75ns + 210ns 이다.

다음으로 multiple SOC 트리거를 통해 다중 ADC 사용시 동기식 동작에 대해 알아보자.

TRM에는 ADC 모듈과 SOCx는 개별적으로 설정할 수 있으나 각 ADC 모듈을 다른 값으로 설정하는 것은 ADCs의 비동기 동작을 유발할 수 있으니 주의하라고 되어있다.

20.13.1.1 장절에 꽤 길게 Basic Synchronous Operation에 대해 설명하고 있다. 요약하면 ADC 변환 과정이 오버랩 되면 ADC가 비동기로 동작하게 되는데 여러 ADC가 활성 변환상태 일 때 한 ADC의 양자화(Quantization) 단계의 내부 노이즈 커플링이 다른 ADC 모듈의 sample and hold 단계에 영향을 미칠 수가 있다고한다. 이로 인해 ADC의 일부 성능이 저하되거나 아예 동작을 하지 않을 수도 있으니 주의하라는 내용이다.

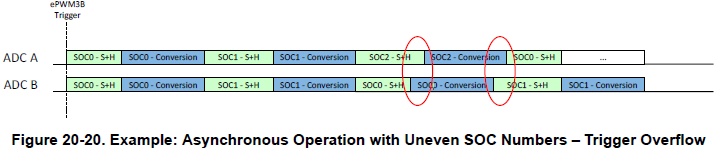

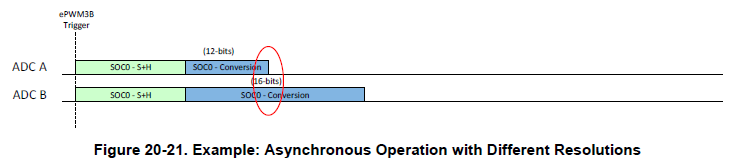

아래 그림에서 초록 부분이 S+H duration 파란부분이 ADC processing Block의 Conversion time이다.

간단하게 말하면 동기식으로 작동하려면 한 ADC 모듈의 각 변환 단의 시작과 끝이 다른 ADC 모듈 시작과 끝 도중에 걸치면 안된다.

사실 그냥 모든 ADCs 모듈에 하나의 트리거 소스를 사용하고, 분해능을 16-bit든 12-bit든 통일하고, ADCCLK를 SYSCLK에서 동일하게 프리스케일하고 모든 SOC의 S+H duration을 동일하게 설정하면 복잡한 고민할 필요가 없다.

아래 그림이 비동기 동작의 예시이다.

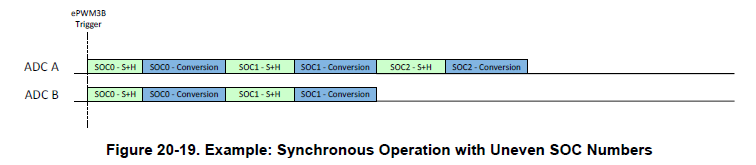

반면 아래 그림들은 전부 동기식 동작의 예시이다. 결국 변환시간의 어긋남으로 인해 다른 ADC 모듈에 영향만 안주면 되는 것이다. 참고로 그림 20-19에서는 ADC-A의 SOC2 변환이 끝난 뒤에 다음 ePWM 트리거가 도착할 것이다.

그리고 여기서 그림 20-19에서 ADC 결과를 획득하는 방식을 생각해보면 ADC-A의 SOC2가 순차 변환 시퀀스의 마지막이므로 ADC-A EOC2 signal을 ADCAINTx 소스로 선택해서 ADCAINTx ISR에서 ADC-A, ADC-B 모듈의 ADCxRESULTx 레지스터에 있는 5개 채널의 변환 값을 한번에 획득할 수 있다.

참고 :

'임베디드 개발 > TMS320F2838x (C28x)' 카테고리의 다른 글

| TMS320F28388D ] Input Qualification (0) | 2024.07.02 |

|---|---|

| ccs 프로젝트 빌드 과정 (0) | 2024.06.12 |

| TMS320F28388D ] Maximum Input Voltage (0) | 2024.04.29 |

| TMS320F28388D ] 부트핀 구성을 바꾸는 법 & SCI boot 모드 사용시 디폴트 TX/RX핀 말고 다른 핀을 사용하는 방법 (0) | 2024.04.10 |

| CCS ] Invalid project path: Missing project folder or file 해결법 (0) | 2024.01.20 |