1. IC 7408의 AND게이트

IC7408 핀배치도

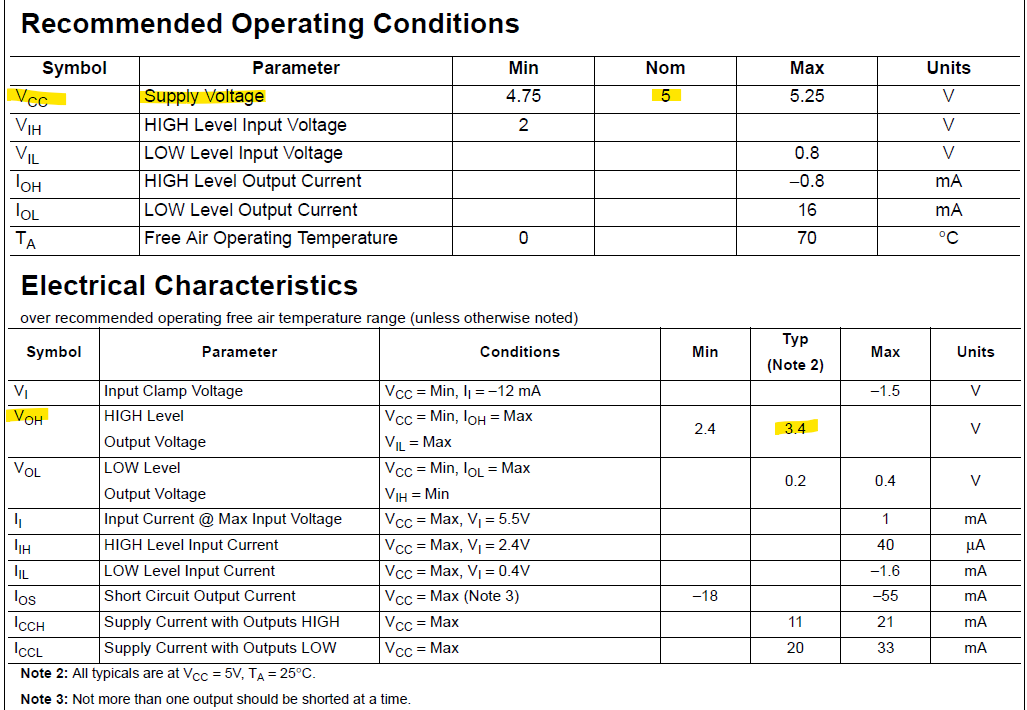

실습시 input에는 아무것도 안꽂고 output에만 선을 꽂아도 불이 들어왔는데 이는 플로팅현상으로 인한 것으로 주변 노이즈에 의해 불이 들어올 수 도 있고 안들어 올 수도 있다. 그러니 반드시 input 에 1 또는 0의 값을 넣어줘야 정확한 결과를 확인 가능하다. 또한 330옴 저항을 사용하였는데 high level output voltage가 3.4V인 것을 감안하면 더 낮은 저항을 써도 될 것 같다.

2. IC 7432의 OR게이트

IC 7432 핀배치도

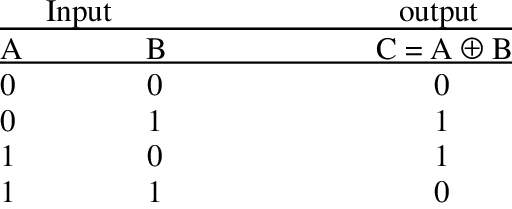

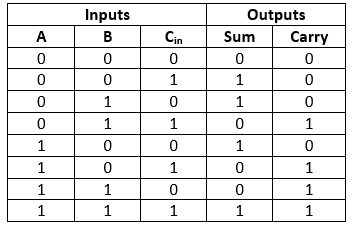

3. IC 7408, 7486, 7432 (AND/XOR/OR) 사용 전가산기 구현

IC 7486 (XOR 게이트) 핀 배치도와 truth table

input으로 A, B, carry-in 을 받고 output으로 sum과 carry-out이 나온다.

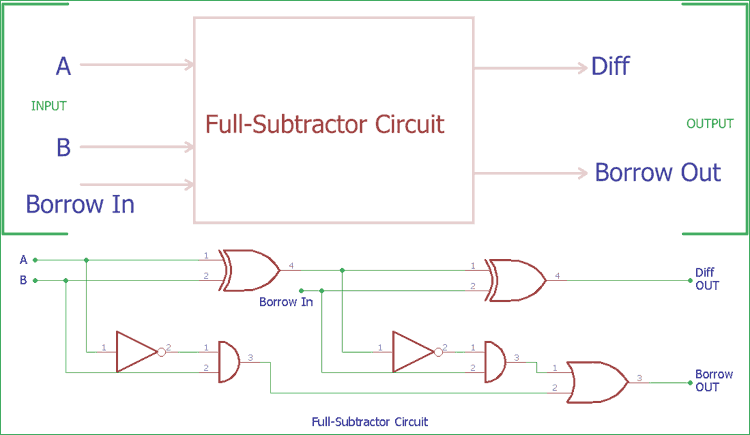

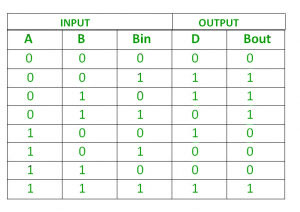

4. IC 7408, 7486, 7432, 7404 (AND/XOR/OR/NOT) 사용 전감산기 구현

input으로 A, B, borrow-in(뒷자리에 빌려줄 것) 이 있고 output으로 sum과 borrow-out(앞자리에서 빌려올 것)이 나온다.

5. IC 7483 사용 4비트 병렬가산기 구현

6. IC 7483, 7486 사용 4비트 병렬가감산기 구현

위 사진에서 K가 0일때 가산기로 작동하고 K가 1일 때 감산기로 작동한다.

XOR 게이트의 진리표와 같이 확인하면 한쪽입력(K)이 0인 경우 반대쪽 입력이 그대로 output으로 나오고, 한쪽입력(K)이 1인경우 반대쪽 입력의 반전이 output으로 나오면서 carry-in에도 1이 입력되므로 B를 2의 보수화해서 더하는 방식으로 뺄셈하게 된다.

C-out는 가산기 일때는 carry out이 맞고

감산기 일때는 위의 반감산기와는 반대로 일반 뺄셈으로 계산하면 borrow발생시 C-out이 0이 나오고 borrow가 발생하지 않으면 1이 나온다.

해석방법도 다른데 C-out이 1이면 C-out을 무시하고 남은 숫자만 보면 되고 C-out이 0이면 다시 2의 보수화해서 부호 절대값으로 바꿔 읽으면 된다. 이는 실제 2의 보수 뺄셈방식과 동일하다.

ex. 10-5 = ?

00001010 - 00000101

00001010 + (11111011)

= 1(자리올림)00000101

자리올림 발생시 앞의 1을 무시하고 결과는 5이다

5-10 = ?

00000101 - 00001010

00000101 + (11110110)

= 11111011

자리올림은 발생하지 않았고 2의 보수화 해서 읽으면 -5 이다

2의 보수는 한 번 하면 부호가 반대로 바뀌고 두 번 하면 -(-x)=x이듯 원래의 수가 된다.

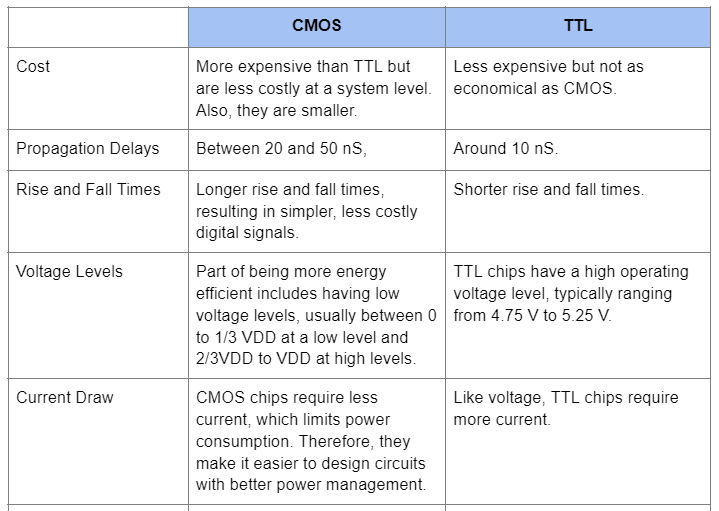

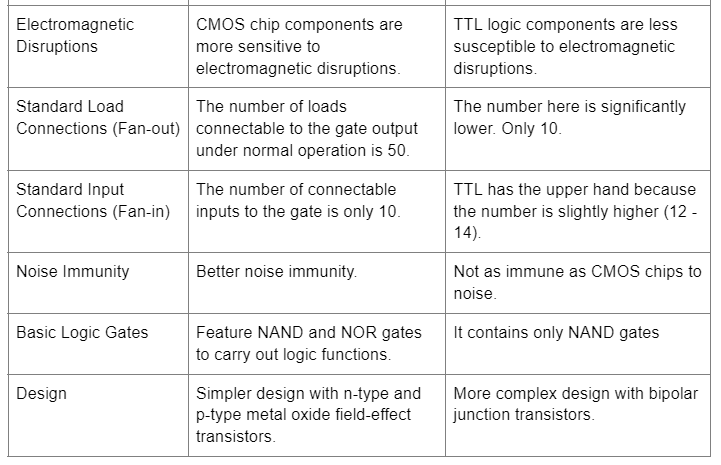

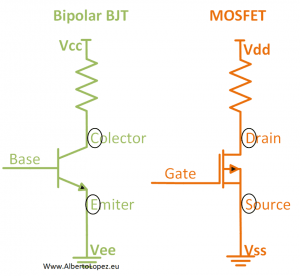

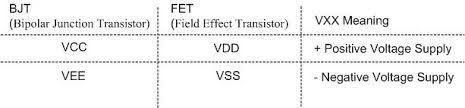

MOSFET(전계효과 트랜지스터)를 사용하는 CMOS 칩과

NPN형 BJT 트랜지스터를 사용하는 TTL 칩의 비교