TMS320F2838x칩 Clock Phase 설정에는 주의할 점이있다.

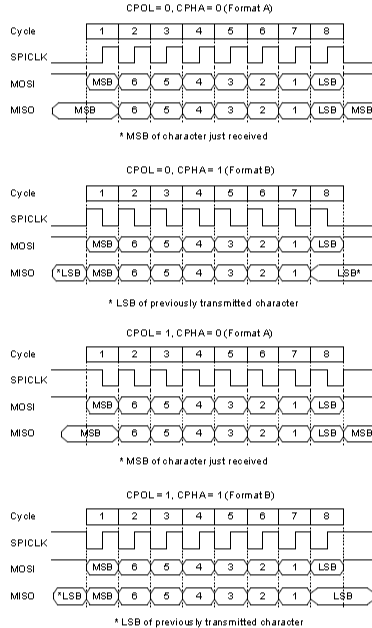

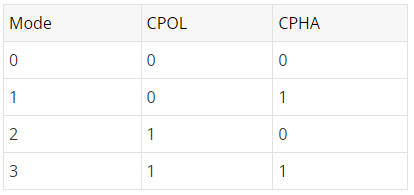

우선 SPI 통신을 하려면 CPOL(Clock Polarity)과 CPHA(Clock Phase)라는 두 가지 파라미터를 설정하는데 이 설정 조합에 따라 다음의 4가지 SPI 모드가 있다.

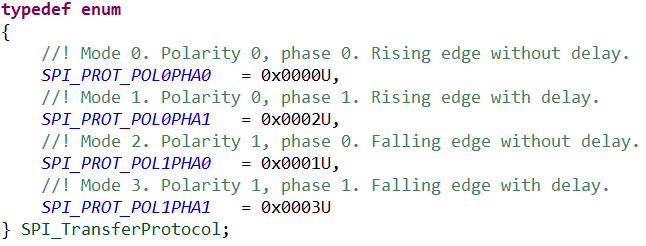

그리고 TMS320F2838x driverlib에도 Mode 설정이 존재하는데 CPOL은 동일하지만, CPHA를 설정할 때 주의가 필요하다.

보통은 CPOL, CPHA 설정에 따라 클럭과 데이터를 동기화하는 방법은 다음과 같다.

- CPOL = 0: IDLE 일 때 클럭이 LOW 레벨이다.

- CPHA = 0 : 데이터가 클럭의 first edge에서 캡쳐(샘플링)되고, 그 다음 edge에서 전파(출력)된다.

- CPHA = 1 : 데이터가 클럭의 second edge에서 캡쳐(샘플링)되고, 그 다음 edge에서 전파(출력)된다.

- CPOL = 1 : IDLE 일 때 클럭이 HIGH 레벨이다.

- CPHA = 0 : 데이터가 클럭의 first edge에서 캡쳐(샘플링)되고, 그 다음 edge에서 전파(출력)된다.

- CPHA = 1 : 데이터가 클럭의 second edge에서 캡쳐(샘플링)되고, 그 다음 edge에서 전파(출력)된다.

그런데 유저매뉴얼 SPI CCR 레지스터 설명을 봐보자.

예를 들어 CLK POLARITY 가 0이고 CLOCK PHASE 가 0일 때 데이터가 상승에지에서 출력되고 하강에지에서 입력된다고 되어있다.

이는 일반적인 CPOL = 0, CPHA = 1 의 동작이니, 즉 CPHA를 반대로 설정해야 의도한대로 동작하는 것이다.

매뉴얼의 SPICLK signal options 그림을 참조하자.

그림 아래 설명에도 CPOL, CPHA 설정은 부품 제조업체마다 다를 수 있으니 아래 waveform을 보고 선택하라고 되어있다.

그러니 Receive latch points를 기준으로 보고 선택하면 되겠다.

실제로도 제어하려는 IC가 mode 3(CPOL = 1, CPHA = 1)을 지원하면, TMS320F2838x 칩에서는 CPOL = 1, CPHA = 0 으로,

IC가 mode 0(CPOL = 0, CPHA = 0)을 지원하면 TMS320F2838x 칩에서는 CPOL = 0, CPHA = 1로 설정해야 통신이 잘 되는 것을 확인하였다.

'임베디드 개발 > TMS320F2838x (C28x)' 카테고리의 다른 글

| TMS320F28388D ] 부트 과정 (0) | 2023.08.16 |

|---|---|

| TMS320F28388D ] Reset Sources (0) | 2023.08.14 |

| TMS320F28388D ] eCAP으로 ePWM 신호 Period와 Duty Cycle 측정 (7) | 2023.08.14 |

| TMS320F28388D ] ECAP (0) | 2023.08.14 |

| W25Q64JV, SPI Interface NOR 플래시 메모리 데이터시트 분석 (2) | 2023.07.24 |