메모리 인터페이스

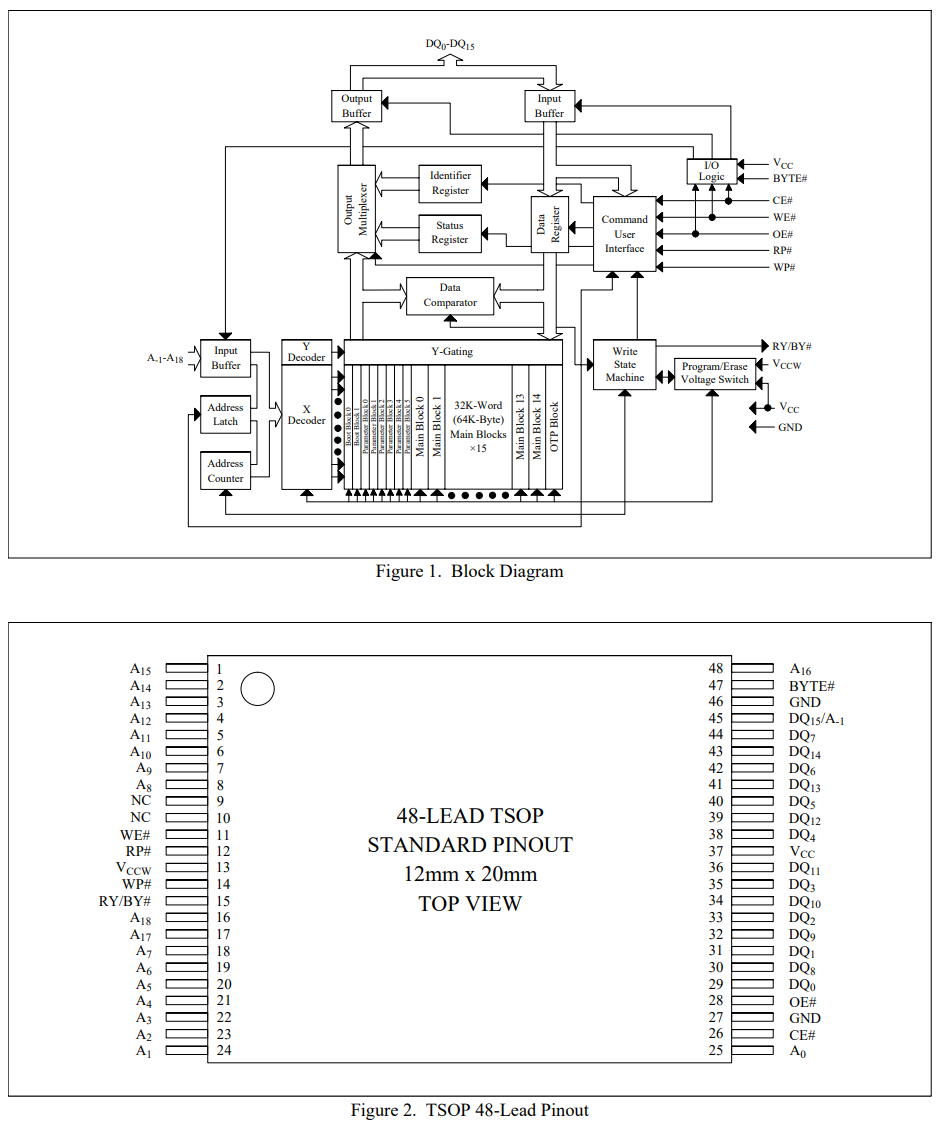

일반적인 메모리의 핀 구성요소는 위의 사진과 같다. Address Pin과 Data Pin으로 구성되어 있고, 칩을 활성화하기 위한CS\(Chip Select 또는 CE)핀이 있고, OE(Output Enable) 신호 핀이 있다.

OE는 읽기 동작에 대한 enable 신호이고, WE(Write Enable)핀이 따로 있는 경우도 있다. 만약 OE핀만 있다면 OE가 logic 1일땐 Read, OE가 0일땐 Write로 동작한다.

위 Flash Memory를 예시로 보면 Address Line은 A0~A18 19개가 있고, 양방향으로 쓰이는 Data Line은 DQ0~DQ15 16가 있다. Data Line이 16개라는 건 한번에 16bit(2Byte)를 읽을 수 있는 메모리라는 뜻이고, Address Line은 19개가 있으니 2^19개 만큼의 Address를 구별해서 input으로 넣을 수 있다는 뜻이다.

즉 이 메모리는 word 가 16bit이고 2^19 Word의 크기를 갖는다고 할 수 있다.

스펙상으로는 512K x 16 parallel Interface NOR Flash 라고 표현하며, 8메가비트(8Mbit)=1메가바이트(1MB)의 저장공간을 가진다.

메모리의 읽기/쓰기 동작은 일반적으로 다음과 같다.

Write

1. CE(Chip Select Enable)를 Low로 만든다.

2. WE(Write Enable)를 High, OE(Output Enable)을 Low로 만든다.

3. Address Line에 쓰고자 하는 binary 주소를 input한다.

4. Data Line에 쓸 값을 입력한다.

5. CE를 high로 만든다.

Read

1. CE(Chip Select Enable)를 Low로 만든다.

2. WE(Write Enable)를 Low, OE(Output Enable)을 High로 만든다.

3. Address Line에 읽고자 하는 binary 주소를 input한다.

4. Data Line의 값을 읽는다.

5. CE를 high로 만든다.

SDRAM의 인터페이스

먼저 RAM은 SRAM(Static RAM)과 DRAM(Dynamic RAM)으로 나뉜다.

SRAM 플립플롭을 이용하여 비트 데이터를 저장하는데 가장 빠른 램의 형태로 외부 지원회로가 거의 필요 없으며 전력 소모가 상대적으로 낮다. 단점은 비트 당 저장 비용이 비싸다.

DRAM은 커패시터 배열을 이용해 비트 데이터를 저장하는데, 커패시터 배열이 전하를 금방 방전해 버리므로 일정 주기로 재충전해주는 과정이 필요하다. 재충전을 위해 부가회로가 필요하며, 재중천 과정으로 인해 프로세서가 메모리를 참조하는 과정이 지연될 수 있다. 장점은 비트 당 저장 비용이 저렴하다.

때문에 컴퓨터에서 캐시가 SRAM으로 구성되고 주 메모리가 DRAM으로 구성된다.

여기서 SDRAM은 Synchronous DRAM으로 비동기식이던 기존 방식과 달리 제어 장치 입력을 클락 펄스와 동시에 일어나도록 해 성능이 향상된 DRAM을 말한다.

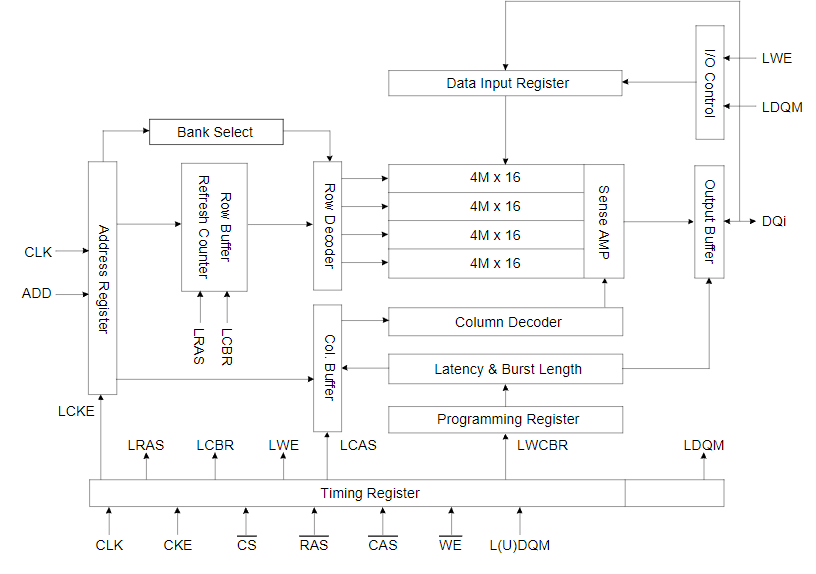

다음 삼성전자의 K4S561632C-TC75 SDRAM datasheet를 참고해보자.

256M bit / 4M*16bit*4banks SDRAM

Data Bus Width가 16bit이고 4M word가 4 banks 있다는 뜻이니 256메가비트(32메가바이트)를 저장할 수 있는 메모리이다.

여기서 TC75는 클럭의 최대 주파수를 말하는 것인데 133MHz를 의미한다.

보통은 프로세서와 SDRAM사이의 TI사의 EMIF와 같은 SDRAM 컨트롤러가 있어 컨트롤러와 SDRAM을 잘 연결하고, 프로세서에 있는 SDRAM 컨트롤러를 제어하는 시스템 레지스터를 조작하여 인터페이스 할 수 있다.

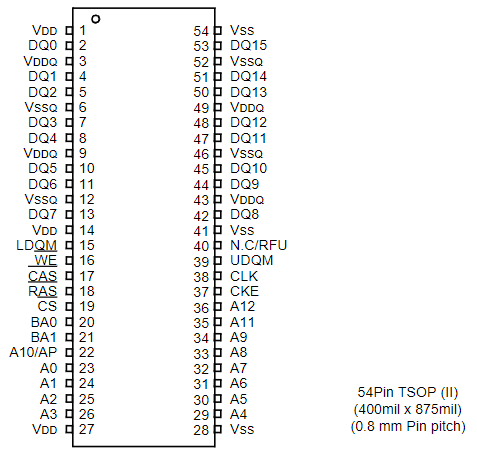

Pin Function

CLK : System Clock. 프로세서에서 생성한 clock input

CS\ : Chip Select. CLK, CKE, DQM 제외 모든 input pin을 enable한다.

CKE : Clock Enable

A0~A12 : Address. Row/Column addresses are multiplexed on the same pins. (Row : A0~A12, Column A0~A8)

BA0~BA1 : Bank Select Pin. Select bank to be activated during row address altch time, Select bank for read/write during column address latch time

RAS\ : Row Address Strobe. Enable row access & precharge

CAS\ : Column address strobe. Enable column access

WE\ : Write Enable. Enable write operation and row precharge.

LDQM, UDQM : Data input/output mask.Upper/Lower bits access 위한 mask

DQ0~DQ15 : Data input/output

Vdd/Vss : Power supply/ground

Vddq/Vssq : Data output power/ground

NC/RFU : No connection/Reserved for future use

SDRAM Interface의 동작 원리

램의 용량이 커질수록 어드레스 핀이 많이 필요하지만 계속해서 핀 수를 늘리면 집적도를 높이고 소형화하는데 불리하다. 그래서 고안된 방법이 메모리를 array로 보고 같은 핀을 멀티플렉싱하여 row와 column 지정에 둘 다 쓰는 것이다. 이를 위해 이 어드레스가 Row쪽인지 Column쪽인지 식별해주는 시그널이 필요하며 해당시그널을 Row Address Strobe, Column Address Strobe, 약자로 RAS, CAS라고 한다.

프로세서가 메모리에 있는 정보를 읽거나 메모리에 정보를 기록할 때는 먼저 가로줄에 RAS신호를 보내고 나서 세로줄에 CAS신호를 보내어 주소를 확인한다. 어떤 주소에 자료가 들어 있는지 아니면 비어 있는 지는 CAS가 담당하며 CAS 신호가 없어지면 그 주소에 다시 새로운 정보를 저장한다.

메모리의 동작 과정을 보면 다음과 같다

1. CPU가 메인보드 칩셋에 데이터를 요청하면 메인보드 칩셋은 그 데이터가 있는 곳의 행(Row, 가로줄) 주소를 메모리로 보낸다. 이것을 하는데는 각각 1 사이클이 걸린다.

2. 행 주소가 메모리의 행 주소 버퍼로 들어오면 센스 앰프(sense amp)가 그 행에 들어있는 모든 셀을 읽어낸다. 이렇게 행 부분을 읽어내는 일을 일으키는 신호는 RAS(row address strobe, 행 주소 스트로브)라고 부르고, 읽는데 걸리는 시간은 RAS-to-CAS delay(RAS와 CAS 사이의 지연 시간)라고 한다. 이 과정은 2∼3 사이클이 걸린다.

3. 행 주소만으로는 필요한 데이터가 어디 있는지 알 수 없으니 이번에는 열(세로 줄) 주소를 받는다. 그러면 CAS(column address strobe, 열 주소 스트로브) 신호가 일어나 정확한 열을 찾아낸다. 이 때 걸리는 시간을 CAS latency(CAS 지연 시간)라고 한다. 이것을 하는데도 역시 2∼3 사이클이 걸린다.

4. 정확한 행과 열을 찾았으니 필요한 데이터를 찾은 셈이다. 메모리 셀에 있는 내용이 출력 버퍼(output buffer)로 옮겨진다. 이것을 하는데는 1 사이클이 걸린다.

5. 마지막으로 메인보드 칩셋이 출력 버퍼의 내용을 읽고 CPU로 전달한다. 이 때 각각 1 사이클씩 모두 2 사이클이 걸린다.

Reference :

'임베디드 개발 > 펌웨어' 카테고리의 다른 글

| FPGA IP (Intellectual Property) Core (0) | 2023.03.31 |

|---|---|

| CAN Bus Load 계산 (0) | 2023.03.20 |

| Fragmentation을 피하기 위한(안전한) UDP payload size (0) | 2023.03.20 |

| UML State Machine (0) | 2023.02.27 |

| 터미널 제어문자 ANSI escape code / 터미널에 글자색 배경색 입히기 (0) | 2023.02.20 |