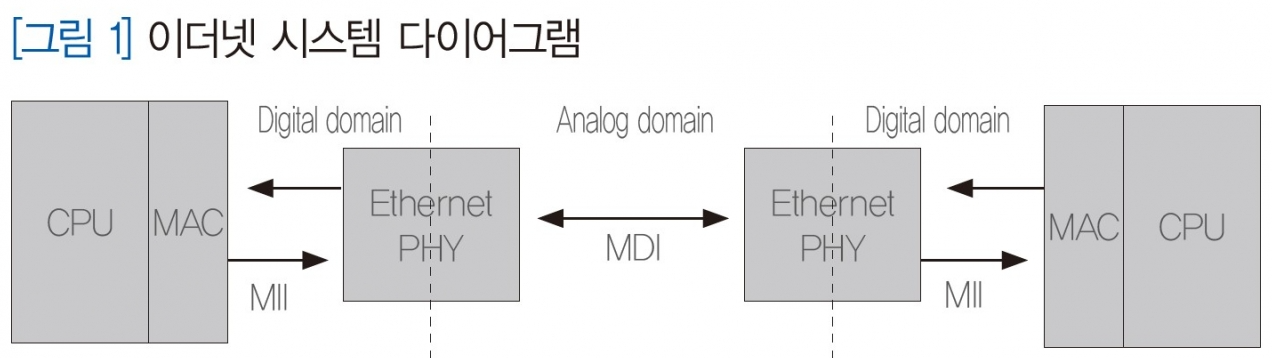

MCU에서 이더넷을 하기 위해 필요한 MAC과 PHY 그리고 MII, RMII에 대해 알아보자

아래 사진은 S/W Block과 H/W Block으로 구성된 OSI 7 Layer 이다.

그 중에 MAC과 PHY는 H/W Block에 위치해 있다. MAC은 데이터 링크 계층, PHY는 물리 계층이다.

TCP/UDP 와 IP 까지는 S/W 에서 Packet을 만든 다음 전송은 MAC 과 PHY 을 통해서 하게 된다.

이때 MAC 에서 PHY로 DATA가 전송하는 통신 방법으로 MII 와 RMII 등이 있다.

전체적인 흐름은 S/W에서 TCP/IP 또는 UDP/IP Packet을 만든 다음 MAC 으로 전달하고, MAC 에서는 추가로 헤더를 붙여 MII 방식을 통해서 PHY 로 전송하면 PHY 는 디지털 데이터를 물리적 전기신호(아날로그 시그널)로 만들어 TX, RX 핀으로 전송한다.

그리고 트랜스포머를 거처 RJ45 잭을 이용해서 전송되게 된다.

출처 : https://blog.naver.com/zelkobaray/222147723016

MAC

MAC 이란 Media Access Control 의 약자로 MAC 주소는 네트워크 통신을 하는 하드웨어에 할당된 고유 주소이다.

PHY

PHY의 기능은 크게 두가지로 구분할 수 있다. MCU, CPU와 같은 MAC 디바이스와 인터페이스 하는 부분이 MII/RMII 이고, 바깥의 물리 매체과 연결되는 부분이 MDI이다. 바깥의 케이블이 구리선이든 광섬유든 10Mbps 또는 100Mbps용 케이블이든 구별하지 않고 MAC을 사용할 수 있게 하는 것이 PHY 트랜시버의 역할이다.

Transformer 와 RJ45 커넥터

트랜스포머는 PHY와 RJ45 커넥터 사이를 연결 시켜주는 마그네틱 모듈이다. 보통은 RJ45 커넥터 내에 트랜스포머와 LED까지 내장되어있다.

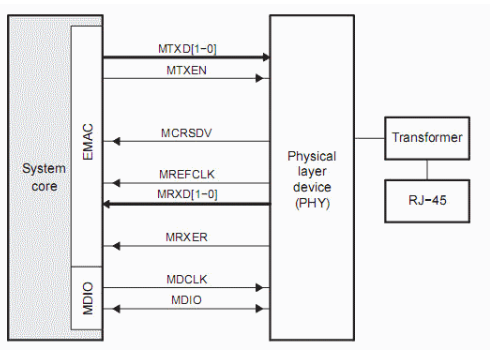

MII

Media Independant Interface 의 약자로 처음 등장한 MAC 과 PHY 인터페이스이다.

TXD[3-0], RXD[3-0] 데이터 버스가 4 bit 이므로 클럭은 25MHz가 공급 되어야 최대 100Mbps로 전송할 수 있다.

저 중에 MDC, MDIO는 PHY칩의 레지스터를 읽고 쓸 수 있는 신호로 PHY칩의 여러가지 기능을 조작할 수 있다. I2C방식과 유사하다고 보면 된다.

이 외 제어 신호는 TXEN (전송 활성화), RXDV (데이터 수신 유효), CRS (Carrier Sense) 등이 있다.

RMII

Reduced MII 의 약자로 MII의 일부 제어 신호를 병합하거나 다중화해 인터페이스의 라인을 줄인 형태이다.

TXD[1-0], RXD[1-0] 데이터버스도 2 bit 씩으로 줄었으므로 100Mbps 전송을 지원하려면 클럭은 50MHz 가 공급되어야 한다.

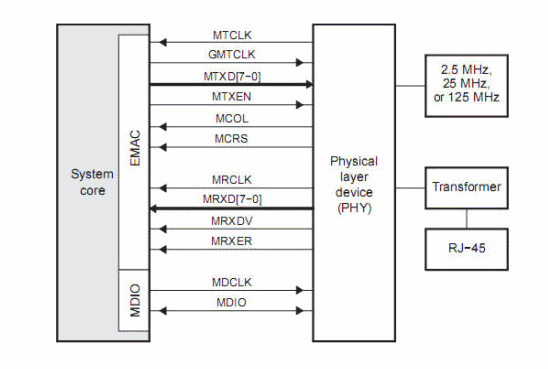

GMII

GMII는 MII의 확장형으로 최대 1Gbps의 데이터를 지원하는 인터페이스이다. 데이터 버스는 TXD[7:0], RXD[7:0]로 8bit씩 사용되며, 125MHz 클럭으로 동작한다. 이로 인해 높은 속도로 데이터 전송이 가능하다.

RGMII

RGMII는 GMII를 간소화한 인터페이스로, 신호선을 줄이기 위해 데이터 전송 시 클럭의 상승/하강 에지에서 데이터를 전송하는 방식(DDR)을 사용한다. 데이터 버스는 TXD[3:0], RXD[3:0]으로 4bit씩이며, 125MHz 클럭으로 동작한다. GMII에 비해 적은 핀 수로 1Gbps 속도를 유지할 수 있다.

'임베디드 개발 > 펌웨어' 카테고리의 다른 글

| ADC (Analog-to-digital converter) (0) | 2022.10.12 |

|---|---|

| LwIP TCP/IP 스택 살펴보기 (0) | 2022.09.24 |

| CPU, MCU, MPU, DSP, FPGA 구분 (0) | 2022.09.10 |

| 빅 엔디안(Big Endian)과 리틀 엔디안(Little Endian) (0) | 2022.08.31 |

| CISC 와 RISC (0) | 2022.06.23 |