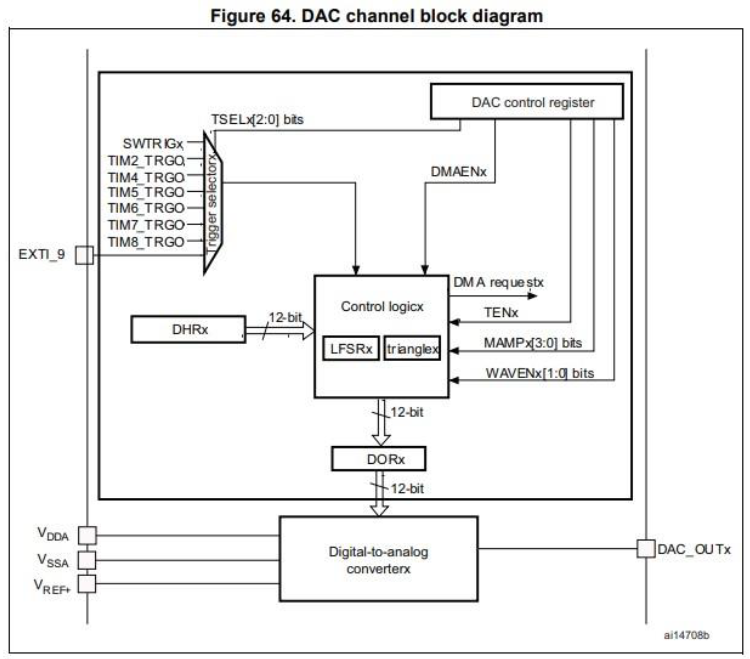

DAC : Digital to Analog Converter 디지털 신호를 아날로그 전압 신호로 변환하여 출력하는 장치를 말한다.

STM32F429 보드는 2채널의 12비트 DAC 컨버터가 있고

DAC CHANNEL_1의 출력핀은 PA4 (DAC_OUT1)

DAC CHANNEL_2의 출력핀은 PA5 (DAC_OUT2)

으로 정해져있다.

1.8v ~Vdda(3.3V) 사이의 별도의 Vref+ 기준전압을 따로 사용할 수도 있고 타이머의 TRGO (트리거 아웃풋)을 사용하는 것도 가능하다.

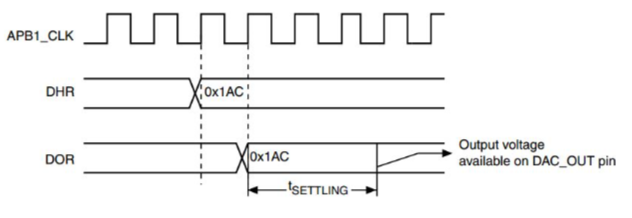

DHR에 로드된 데이터는 ABP1 1클럭 사이클 후 DOR 레지스터로 전송되고 데이터가 DOR 레지스터에 로드되면 DAC변환이 시작되어, t(SETTING) 시간 후 DAC_OUT pin을 통해 아날로그 값이 출력된다.

DAC의 출력전압은 0 ~ Vref+ 사이의 값을 가지며 다음과 같이 결정된다.

설정

소스코드

/* USER CODE BEGIN 2 */

HAL_DAC_Start(&hdac, DAC_CHANNEL_1);

HAL_DAC_Start(&hdac, DAC_CHANNEL_2);

uint32_t dac_value1=0;

uint32_t dac_value2=0;

/* USER CODE END 2 */

/* USER CODE BEGIN WHILE */

while (1)

{

HAL_DAC_SetValue(&hdac, DAC_CHANNEL_1, DAC_ALIGN_12B_R, dac_value1);

HAL_DAC_SetValue(&hdac, DAC_CHANNEL_2, DAC_ALIGN_8B_R, dac_value2);

if(dac_value1<4096){

dac_value1++;

}else{

dac_value1=0;

}

if(dac_value2<256){

dac_value2++;

}else{

dac_value2=0;

}

HAL_Delay(1);

/* for(dac_value=0; dac_value<=255; dac_value++){

HAL_DAC_SetValue(&hdac, DAC_CHANNEL_2, DAC_ALIGN_8B_R, dac_value);

HAL_DAC_Start(&hdac, DAC_CHANNEL_2);

HAL_Delay(1);

}*/

/* USER CODE END WHILE */

/* USER CODE BEGIN 3 */

}

딜레이를 주지 않았을 때 파형

LED는 계속 켜있는 것처럼 보인다.

1ms 딜레이를 주었을 때

아래는 디버그 모드로

레지스터를 살펴본 것. DOR은 HAL_DAC_GetValue() 함수로도 확인 가능하다.

DAC 데이터 포맷

출처 : https://blog.naver.com/sees111/222345571373

단일(Single) DAC 채널

8비트 오른쪽 정렬 : DAC_DHR8Rx[7:0] 비트에 데이터 로드 (데이터 저장은 DHRx[11:4] 비트)

12비트 왼쪽 정렬 : DAC_DHR12Lx[15:4] 비트에 데이터 로드 (데이터 저장은 DHRx[11:0] 비트)

12비트 오른쪽 정렬 : DAC_DHR12Rx[11:0] 비트에 데이터 로드 (데이터 저장은 DHRx[11:0] 비트)

듀얼(Dual) DAC 채널

8비트 오른쪽 정렬

채널1 : DAC_DHR8RD[7:0] 비트에 데이터 로드 (데이터 저장은 DHR1[11:4] 비트)

채널2 : DAC_DHR8RD[15:8] 비트에 데이터 로드 (데이터 저장은 DHR2[11:4] 비트

12비트 왼쪽 정렬

채널 1 : DAC_DHR12LD[15:4] 비트에 데이터 로드 (데이터 저장은 DHR1[11:0] 비트)

채널 2: DAC_DHR12LD[31:20] 비트에 데이터 로드 (데이터 저장은 DHR2[11:0] 비트)

12비트 오른쪽 정렬

채널 1 : DAC_DHR12RD[11:0] 비트에 데이터 로드 (데이터 저장은 DHR1[11:0] 비트)

채널 2 : DAC_DHR12RD[27:16] 비트에 데이터 로드 (데이터 저장은 DHR2[11:0] 비트

'임베디드 개발 > STM32 (ARM Cortex-M)' 카테고리의 다른 글

| STM32 ] BLDC 모터 제어 - 프로젝트 준비과정 (4) (7) | 2022.07.19 |

|---|---|

| STM32 ] 초음파 센서로 거리재기 Timer Input Capture 사용 + 노이즈 (튀는 값) 제거 (5) | 2022.07.18 |

| STM32 ] ADC + MFC + MySQL, 시리얼 통신 및 DB연동, 검색기능, 실시간 그래프 구현 (쓰레드 사용) (1) | 2022.07.17 |

| STM32 ] SysTick Timer Callback 함수 사용하기 (0) | 2022.07.14 |

| STM32 ] 소프트웨어적으로 Chattering 채터링현상 Debounce 디바운싱하기 (0) | 2022.07.13 |