다음 영상을 참고로함:

https://www.youtube.com/watch?v=Yjl7pEsUxYQ&t=158s

데이터 전송 속도 계산 시 고려사항

1. 데이터 레인 수에 따른 대역폭 분산

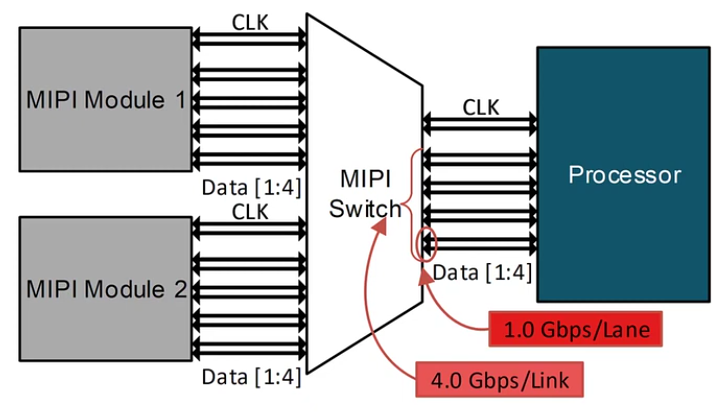

MIPI DPHY는 차동 신호(Differential Signaling)를 기반으로 1~4 lane 구성이 가능하며, 이러한 Data Lane들은 병렬로 동작하여 전체 링크의 총 대역폭을 분산 처리하게 된다.

예를 들어, 전체 데이터 전송 시 필요 대역폭이 4 Gbps이고 4-lane 구성이라면, per Lane 데이터 처리량은 1 Gbps/Lane으로 계산된다.

즉, Lane 수를 늘리면 동일한 총 대역폭을 더 많은 레인에 분산시킬 수 있으므로, 각 레인당 데이터 처리 부담이 줄어들고 레인당 클럭 속도를 낮출 수 있으며, 전력 소비가 감소하고 신호 품질 관리가 용이해지는 장점이 있다.

2. DDR(Double Data Rate)

MIPI D-PHY는 클럭의 Rising edge과 Falling edge 모두에서 데이터가 샘플링되는 DDR 방식으로 동작한다. 즉, 1 클럭 주기 동안 2비트 전송이 가능하므로 시스템 설계 시 클럭 주파수는 요구되는 레인 당 Data Rate의 절반 수준으로 설정할 수 있다.

ex. 1 GHz CLK for 2 Gbps

데이터 전송 속도 계산: 1600 × 2560 @ 60fps, RGB888, DPHY 4-lane 기준

- 조건

- 해상도: 1600 × 2560

- 프레임 레이트: 60 fps

- 포맷: RGB888 (8 bits per channel × 3 channels = 24 bits per pixel)

- MIPI D-PHY

- 데이터 레인 수: 4 lane

1. Pixel Clock 계산

1600 x 2560 x 60 = 245.8 Mpixel/sec

2. Total Bit 전송률 계산

245.8 Mpixels/sec × 24 bits/pixel = 5.9 Gbps (링크 전체 기준)

3. Lane 수에 따른 Data rate 분배

5.9 Gbps ÷ 4 lanes = 1.5 Gbps/lane

4. 설계 마진 고려

비디오 블랭킹 구간과 오버헤드 고려한 1.5x ~ 3x 정도의 마진 적용 후 Lane 당 요구 대역폭과 클럭 주파수(대역폭 * 1/2)

2.2 Gbps to 4.4 Gbps / 1.1 GHz to 2.2 GHz

※ 위 계산에서 1.5x ~ 3x의 설계마진이 필요한 이유는?

MIPI CSI-2는 HSYNC, VSYNC 펄스 신호 대신 데이터 스트림 내의 패킷 구조(SoT/EoT)를 통해 동기화한다. 이 과정에서 패킷 헤더, 푸터, CRC 등 프로토콜 오버헤드가 생긴다. 또한 D-PHY 특성 상 LP와 HS 모드를 전환하는 시간도 추가로 소요된다. 한편, 송신자인 카메라 센서 쪽에서도 내부 데이터 변환 및 동기화 유지를 위한 물리적인 유휴 시간이 반드시 발생한다. 따라서 한 프레임 기준 주어진 시간 중 실제 데이터를 송신할 수 있는 순수 가용 시간은 일부이며, 제한된 시간 안에 전체 픽셀 데이터를 모두 전송하려면 순수 계산 대역폭보다 훨씬 높은 속도로 데이터를 쏴줘야한다. 따라서 이를 고려한 마진을 넣어 Lane당 전송 속도를 높게 잡는 것이다.

다만, 위의 자료는 일반적인 설계 기준을 단순화해 설명한 것이며 실제 시스템 설계에서는 훨씬 더 복합적인 고려가 필요할 것이다.

'임베디드 개발 > 펌웨어' 카테고리의 다른 글

| MIPI D-PHY (with IMX219 Waveform) (0) | 2025.09.21 |

|---|---|

| Video Timing (+ VESA) (0) | 2025.09.09 |

| USB 2.0 vs USB 3.x 차이 및 핀아웃 (0) | 2025.09.03 |

| GMSL2와 FPD-Link III (0) | 2025.09.01 |

| SN65DP141 ] DisplayPort Redriver (0) | 2025.08.30 |