반응형

OpenVPX 커넥터 구조 및 핀 맵핑 방식 (3U 기준)

이번 글에서는 OpenVPX 3U 기준의 커넥터 구조에 대해 살펴보도록 한다.

1. 커넥터 타입

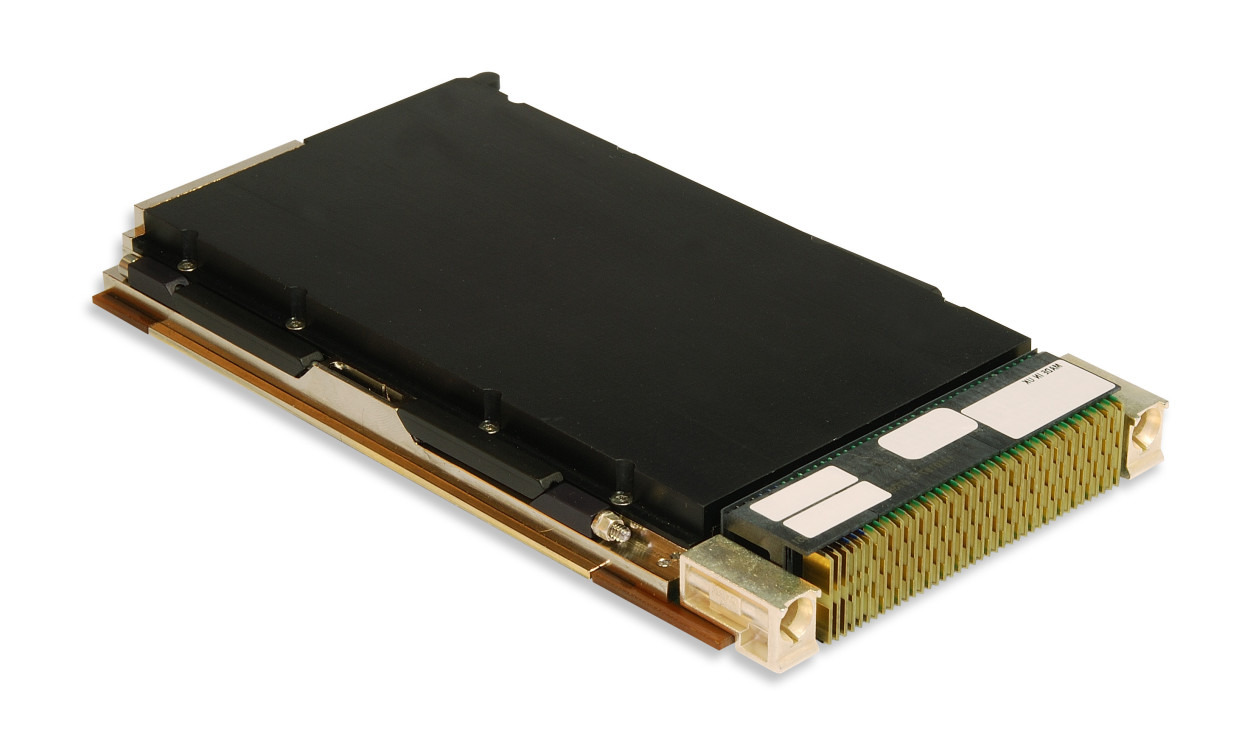

- 플러그(Plug-In Module Connector) : 보드(PCB) 쪽에 장착됨

- 리셉터클(Backplane Receptacle Connector) : 백플레인(Backplane) 쪽에 장착됨

보드(플러그)가 백플레인(리셉터클)에 위에서 아래로 꽂히는 구조.

2. 핀 배열 체계 (Row & Column)

- 하나의 핀은 Row(행)와 Column(열) 조합으로 표현된다.

- Row는 알파벳 문자(대소문자 구분)를 사용하고 Column은 숫자를 사용한다.

- 커넥터에서 짧은 쪽이 Row이다.

- 커넥터에서 긴 쪽이 Column이다.

2.1 Row

| 위치 | 사용 Row | 비고 |

| 플러그(보드) | A, B, C, D, E, F, G | 대문자 (A~G) 사용 |

| 리셉터클(백플레인) | a, b, c, d, e, f, g, h, i | 소문자 (a~i) 사용 |

2.2 Column

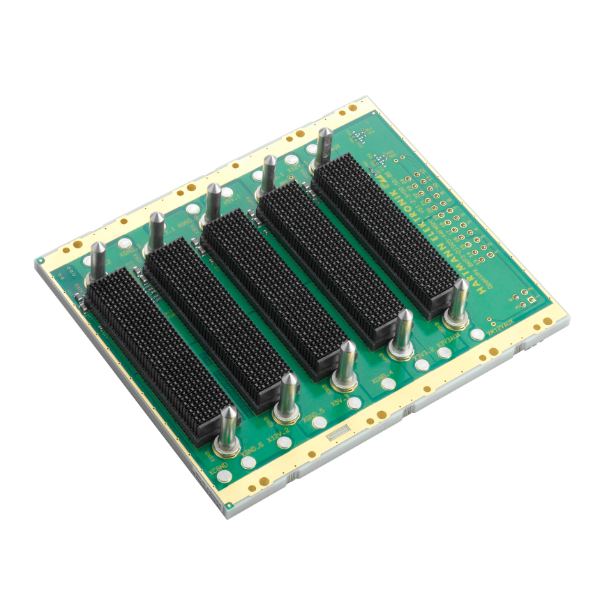

- 3U VPX는 P0 + P1 + P2 세 슬롯으로 구성된다.

- Column(열)은 슬롯마다 번호가 독립적으로 매겨진다.

| 슬롯(Slot) | Column 범위 | 주 용도 |

| P0 슬롯 | Column 1 ~ 8 | 전원(Power) 및 관리신호(Management Signals) |

| P1 슬롯 | Column 1 ~ 16 | 고속 데이터용 (Differential Signals) |

| P2 슬롯 | Column 1 ~ 16 | 추가 고속 데이터용 |

- Column 번호는 Odd/Even을 구분한다.

- Odd (홀수 번호) : 1, 3, 5, 7, 9, ...

- Even (짝수 번호) : 2, 4, 6, 8, 10, ...

3. Wafer 종류

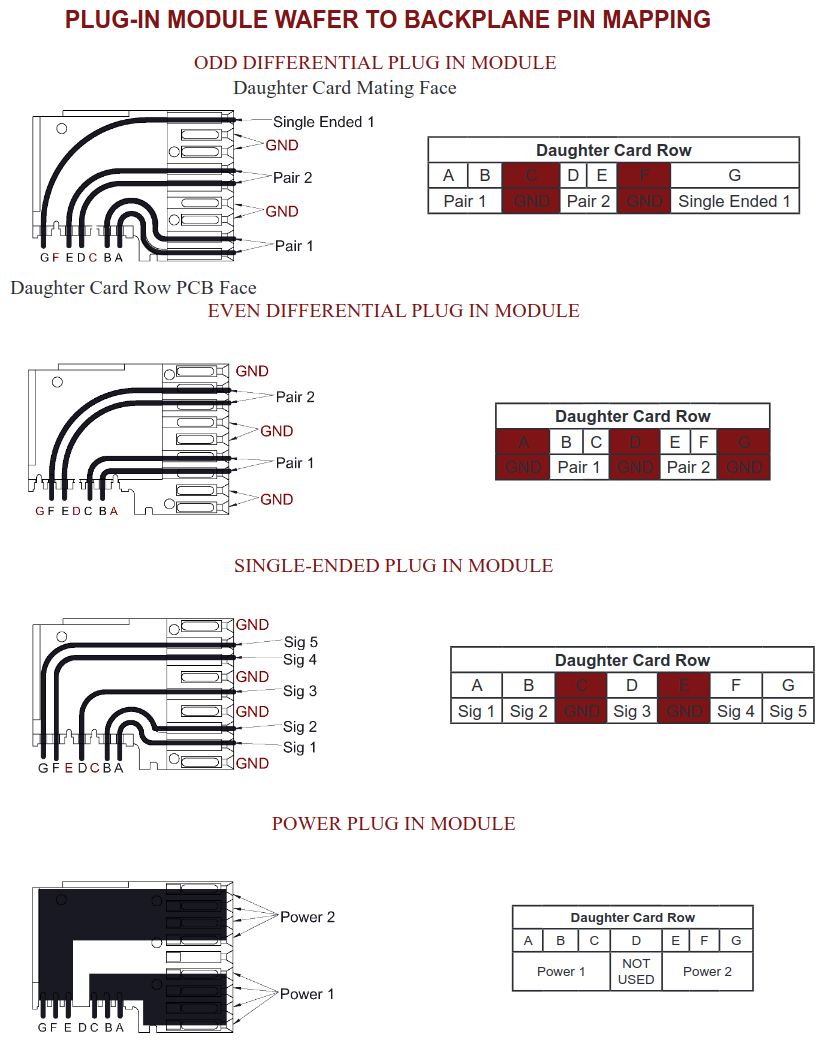

- 플러그 타입 커넥터에 들어가는 Wafer의 종류는 4가지이다.

| Wafer 종류 | 설명 | 주 배치 슬롯 |

| Odd Differential Wafer | 홀수 컬럼용 Differential Pair 신호용 | P1, P2 |

| Even Differential Wafer | 짝수 컬럼용 Differential Pair 신호용 | P1, P2 |

| Single-Ended Wafer | Single-Ended 신호용 | P0 |

| Power Wafer | 전원 공급용 | P0 |

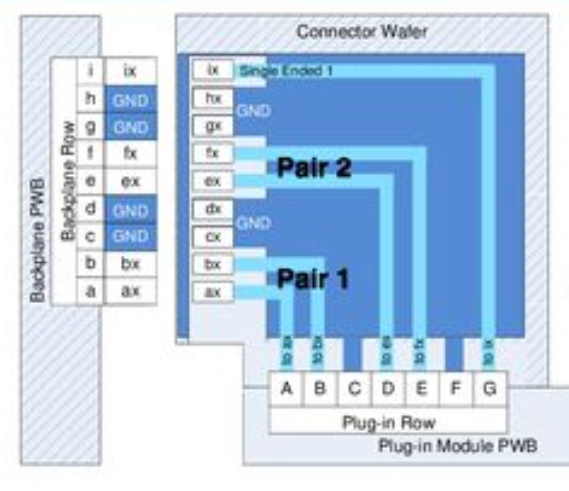

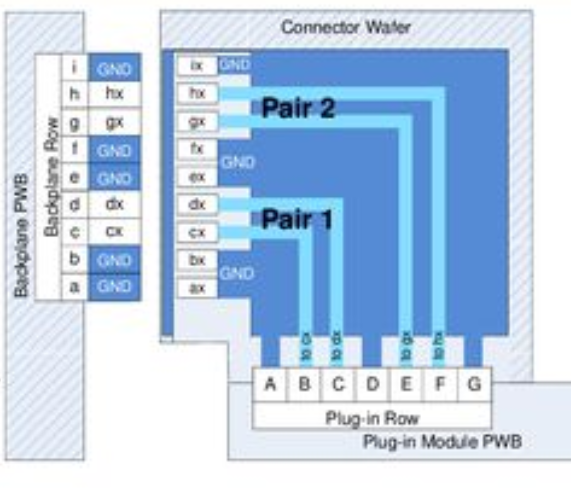

❗️아래 그림을 보면 P1, P2에 배치되는 Odd Differential Wafer와 Even Differential Wafer는 리셉터클과 연결되는 배선 방식이 서로 다르다는 것을 알 수 있다.

4. 핀 맵핑 방식

4.1 Odd Differential Wafer 매핑

| Plug-In(보드) Row | Receptacle(백플레인) Row |

| A | a |

| B | b |

| D | e |

| E | f |

| G | i |

- 나머지 Row들은 Ground 처리

4.1 Even Differential Wafer 매핑

| Plug-In(보드) Row | Receptacle(백플레인) Row |

| B | c |

| C | d |

| E | g |

| F | h |

- 나머지 Row들은 Ground 처리

❓️ 왜 Odd Column과 Even Column의 웨이퍼를 구분하고 배선 방식을 다르게 가져갈까?

이는 Signal Integrity(SI) 최적화를 위해서 신호 간섭(Crosstalk)을 줄이려는 목적이다.

고속 신호들이 옆 라인과 간섭을 일으키면 신호 품질에 문제가 생길 수 있다. 이를 막기 위해 Differential Pair 간에는 항상 GND를 끼워 넣어서 차폐(Shielding)를 하고, 신호선이 서로 이웃하지 않는 Odd 웨이퍼와 Even 웨이퍼를 교차로 배치해서 신호 간 영향을 최소화하는 것이다.

반응형

'임베디드 개발 > 펌웨어' 카테고리의 다른 글

| HDMI (Hot Plug, DDC, EDID) (0) | 2025.05.20 |

|---|---|

| PowerPC (0) | 2025.05.09 |

| 최적의 I2C 풀업 저항 선택 방법 (0) | 2025.04.27 |

| RJ-45 커넥터 핀아웃 (10/100BASE-T, 1000BASE-T 연결 방법) (0) | 2025.04.15 |

| DAC sine wave 생성 (0) | 2025.04.12 |