88E1512 데이터시트 분석

1. 제품 개요

Marvell의 Alaska 88E1512는 기가비트 이더넷 PHY(PHYsical Layer Transceiver)로, RGMII 또는 SGMII MAC 인터페이스를 지원하며 10/100/1000BASE-T를 지원한다.

2. 88E151x 시리즈 모델별 차이

이 중 88E1512는 RGMII 또는 SGMII MAC 인터페이스를 지원하며, Copper와 Fiber 연결을 모두 처리할 수 있고 Auto-Media Detect 기능과 다양한 I/O Voltage 지원으로 이 시리즈 중에서는 가장 범용성이 좋다.

Auto Media Detect 기능은 Fiber 포트에 광 모듈 꽂으면 자동으로 Fiber 모드로 전환하고 RJ45에 케이블 꽂으면 자동으로 Copper 모드로 전환해주는 기능이다.

🔍 RGMII란?

RGMII(Reduced Gigabit Media Independent Interface)는 TX/RX 데이터를 DDR(Double data rate, 상승/하강 엣지) 방식으로 전송하여 GMII 대비 핀 수를 절반으로 줄인 버전이다.

🔍 SGMII란?

SGMII(Serial Gigabit Media Independent Interface)는 MAC과 PHY 간의 고속 직렬 통신 인터페이스로, 10/100/1000BASE-T를 모두 지원하지만 MAC과의 직렬 링크는 항상 1.25Gbps 고정 속도로 동작한다. 클럭과 데이터가 동일한 라인을 통해 전송되기 때문에 클럭 핀이 따로 없으며, 핀 수가 적어 설계가 간편하다.

2. 블록 다이어그램

88E1512의 블록 다이어그램은 다음과 같은 구성으로 이뤄져 있다.

왼쪽이 아날로그 신호를 처리하는 물리 계층(PHY) 블록이고, 오른쪽이 MAC과 연결되는 디지털 인터페이스 블록이다.

3. 핀아웃

88E1512는 56핀 QFN (8mm x 8mm) 패키지로 제공되며, 주요 핀은 다음과 같다.

- 인터페이스 핀

- RGMII/SGMII 핀 : TXD[3:0], RXD[3:0], TX_CLK, RX_CLK, TX_CTRL, RX_CTRL

- SGMII 시리얼 I/O 핀 : S_INP/N, S_OUTP/N

- MDC / MDIO 핀 : 레지스터 제어 및 관리 인터페이스

- 설정 핀

- CONFIG 핀 : 부트스트랩용, PHY 주소 및 VDDO 전압 설정 가능

- RESETn : Active-low 리셋 입력

- LED[0~2] : 동작 상태 LED 출력, LED[2]는 INTn 출력

- 전원 핀

- VDDO (I/O 전압): 1.8V / 2.5V / 3.3V 지원

- DVDD, AVDD33, AVDD18 : 디지털 및 아날로그 코어 전원

- REG_IN / REGCAP1/2 : 내부 레귤레이터용 구성 핀

4. 부트스트랩 핀

해당 칩은 RESETn 신호가 풀렸을 때 CONFIG 핀(Pin 15)이 어디에 연결되어 있냐에 따라 일부 설정이 결정된다.

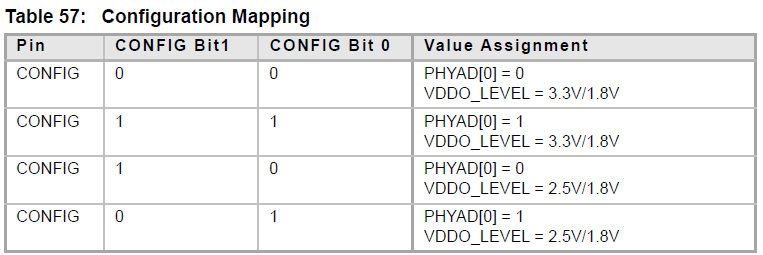

아래 Mapping Table이 있는데, 예를 들어 CONFIG 핀이 VSS에 연결되어 있으면 PHYAD[0] = 0이고, VDDO_LEVEL = 3.3V/1.8V이다.

아마 VDDO는 1.8V는 어느 쪽이든 동작 가능하고 3.3V / 2.5V 둘 중 하나를 고를 수 있게 해둔 것 같다.

그리고 PHYAD는 전체 5비트인데 [4:1] = 0000이라서 PHY 주소는 0 아니면 1이다. PHY 주소는 CONFIG핀으로만 결정되고 레지스터 제어로 변경할 수는 없다.

5. 디바이스 트리 설정 예시

ethernet@2310000 {

status = "okay";

nvidia,mac-addr-idx = <0>;

nvidia,phy-reset-gpio = <&tegra_main_gpio TEGRA234_MAIN_GPIO(G, 5) 0>;

phy-mode = "rgmii-id";

phy-handle = <&phy>;

nvidia,max-platfrom-mtu = <8000>;

nvidia,pause_frames = <0>; /* 0=enable, 1=disable */

mdio {

compatible = "nvidia,eqos-mdio";

#address-cells = <1>;

#size-cells = <0>;

phy: phy@0 {

reg = <0>;

nvidia,phy-rst-pdelay-msec = <224>; /* msec */

nvidia,phy-rst-duration-usec = <10000>; /* usec */

interrupt-parent = <&tegra_main_gpio>;

interrupts = <TEGRA234_MAIN_GPIO(G, 4) IRQ_TYPE_LEVEL_LOW>;

marvell,copper-mode;

/* Setup LED[2] as interrupt pin (active low) */

marvell,reg-init = <0x03 0x12 0x7fff 0x880>;

};

};

};

저 중에서 marvell,reg-init 속성이 PHY 초기화 시 특정 레지스터 값을 설정하는 역할을 한다.

marvell,reg-init = <0x03 0x12 0x7fff 0x880>;

해석하면 다음과 같다.

- 0x03 : 페이지 번호 3

- 0x12 : 레지스터 주소 18

- 0x7fff : 비트 마스크, 하위 15비트만 씀

- 0x880 : 쓸 값은 0x880

- 즉, Page 3 Register 18에서 하위 15비트를 0x880으로 씀

레지스터 맵을 보면 이 설정은 LED[2]를 INTn으로 사용하고, active low로 설정하는 내용이다.

그리고 데이터시트를 보면 MAC 인터페이스 모드를 설정하는 Page 18, Register 20의 MODE[2:0] 비트는 88E1512의 경우 디폴트 값이 Reserved인 111이라서 반드시 프로그램되어야 한다고 나와있다.

그런데 디바이스 트리 상에는 INT핀 설정만 명시적으로 하고, MODE 설정은 따로 레지스터 초기값 속성을 쓰고 있지 않다. 아마도 그 이유는 phy-mode 속성에서 "rgmii-id" 값을 읽어 드라이버에서 자동으로 설정하는 듯 하다.

그리고 DT에 따로 compatible 속성이 안보이는데 이는 커널 부팅 시 MDIO 스캔을 통해 PHY ID를 읽어오고 ID를 기반으로 자동으로 해당 드라이버를 로드하기 때문이다.

- 드라이버 위치 : /drivers/net/phy/marvell.c

DT 설정 참고 링크 :

https://forums.developer.nvidia.com/t/does-orin-support-88e1512-phy-chip/215951/17

'임베디드 개발 > 펌웨어' 카테고리의 다른 글

| USB 플래시 드라이브와 SD카드의 동작 방식 (0) | 2025.07.21 |

|---|---|

| MIPI CSI-2 (0) | 2025.07.12 |

| ADS1015 데이터시트 분석 및 Tested on Raspberry Pi (0) | 2025.06.09 |

| VPX, OpenVPX, SOSA 정의 및 주요 표준 신호 (0) | 2025.06.04 |

| HDMI (Hot Plug, DDC, EDID) (0) | 2025.05.20 |